# MetaStable State (3E)

Young Won Lim 6/29/13 Copyright (c) 2011-2013 Young W. Lim.

Permission is granted to copy, distribute and/or modify this document under the terms of the GNU Free Documentation License, Version 1.2 or any later version published by the Free Software Foundation; with no Invariant Sections, no Front-Cover Texts, and no Back-Cover Texts. A copy of the license is included in the section entitled "GNU Free Documentation License".

Please send corrections (or suggestions) to youngwlim@hotmail.com.

This document was produced by using OpenOffice and Octave.

Meta (from the Greek preposition  $\mu\epsilon\tau\dot{\alpha}$  = "after", "beyond", "adjacent", "self", also commonly used in the form  $\mu\epsilon\tau\alpha$ - as a prefix in Greek, with variants  $\mu\epsilon\tau$ - before vowels and  $\mu\epsilon\theta$ - "meth-" before aspirated vowels), is a prefix used in English (and other Greek-owing languages) to indicate a concept which is an abstraction from another concept, used to complete or add to the latter.

For example, metadata are data about data (who has produced them, when, what format the data are in and so on).

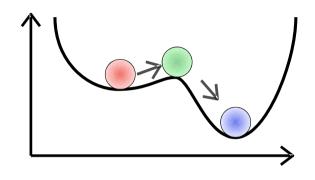

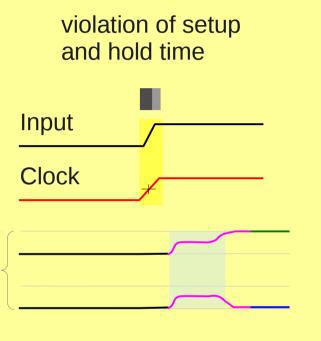

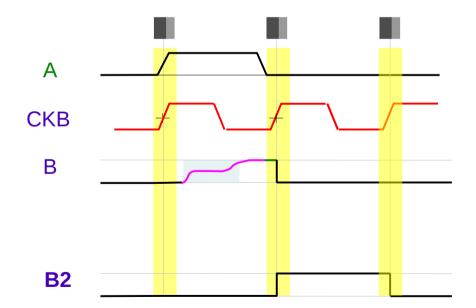

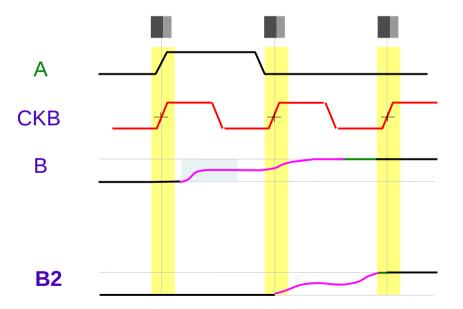

Metastability in electronics is the ability of a digital electronic system to persist for an unbounded time in an unstable equilibrium or metastable state.

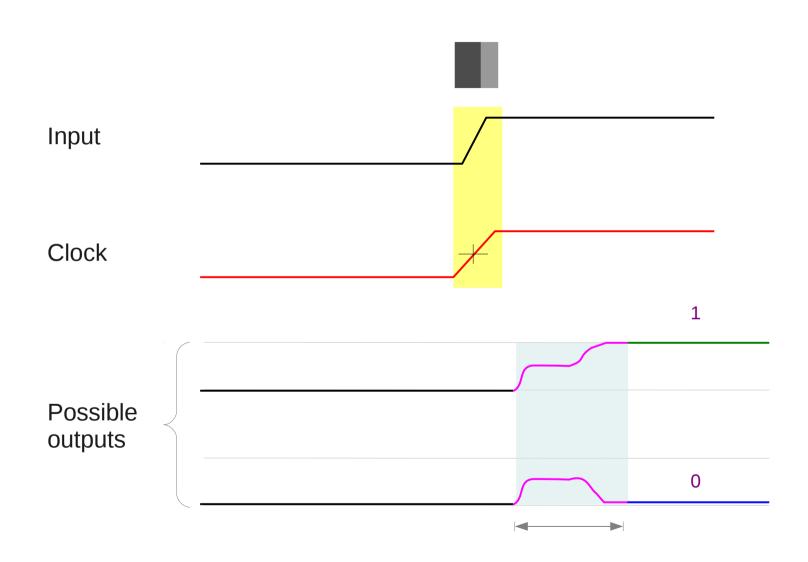

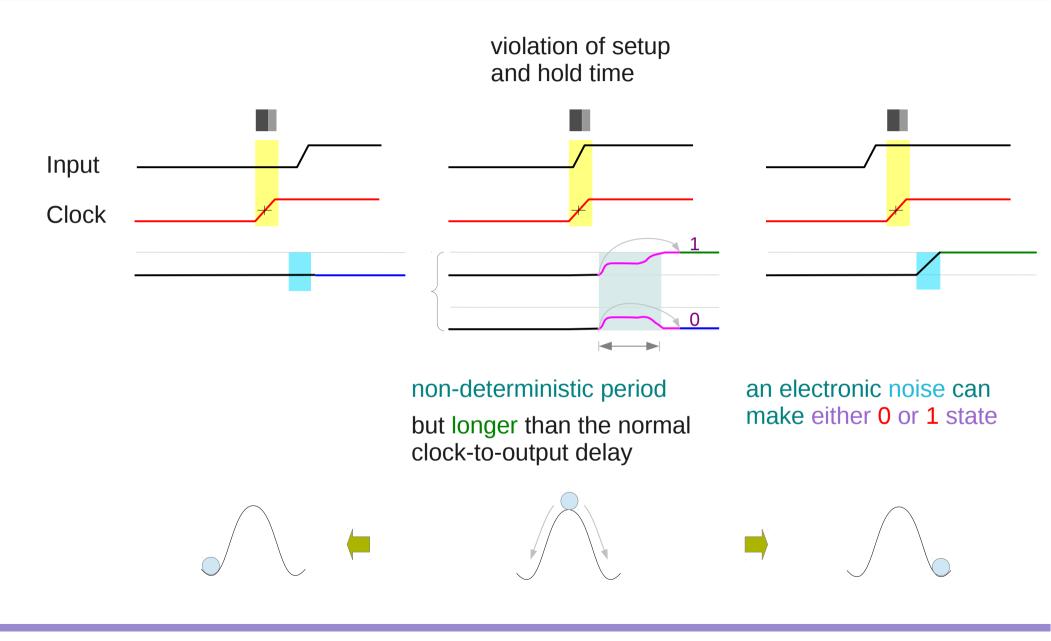

In metastable states, the circuit may be <u>unable</u> to settle into a stable '0' or '1' logic level <u>within</u> the time required for proper circuit operation.

As a result, the circuit can act in unpredictable ways, and may lead to a system failure, sometimes referred to as a "glitch".

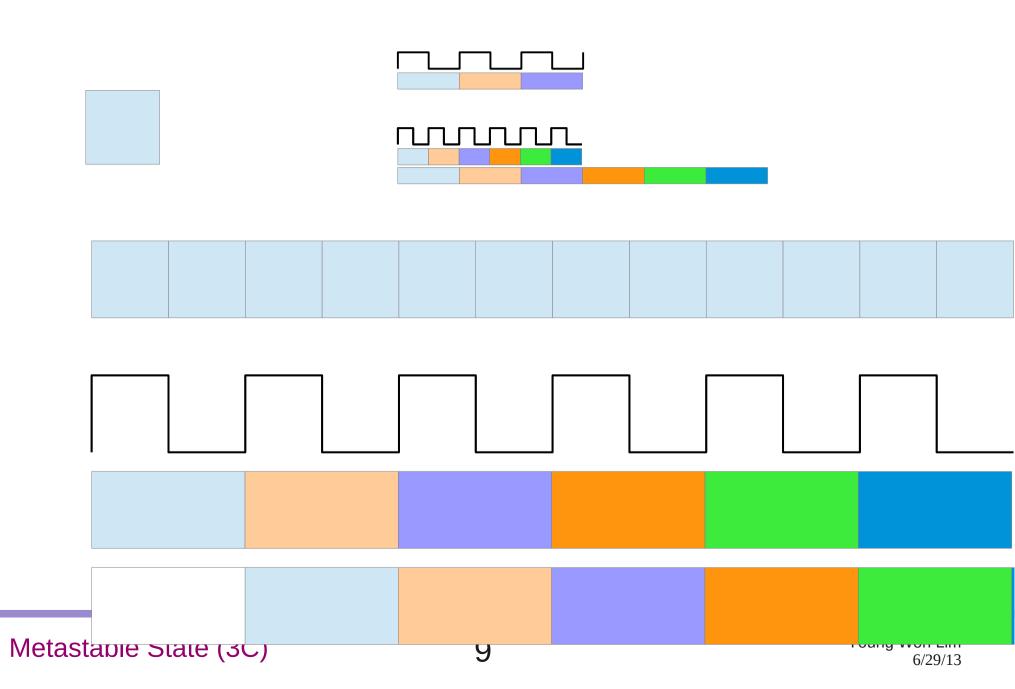

### **Possible Metastable Outputs**

Metastable State (3C)

# Metastability

6

#### Metastable State (3C)

Young Won Lim 6/29/13

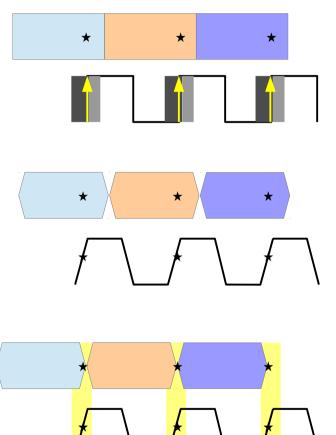

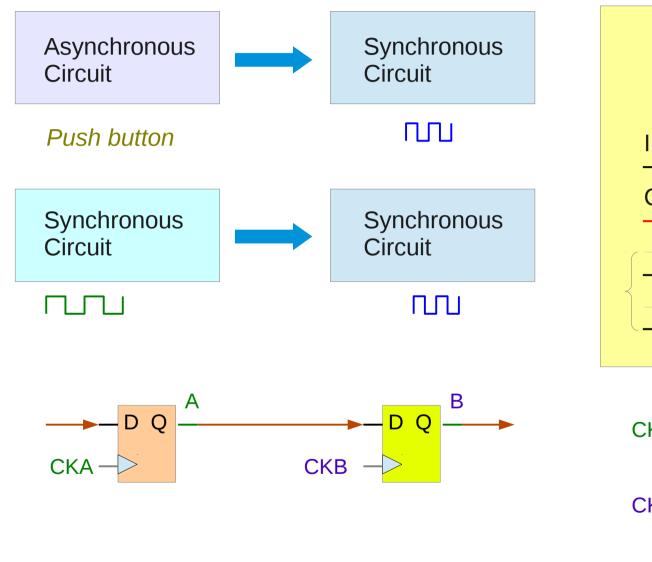

### **Causes of Metastability**

Metastable State (3C)

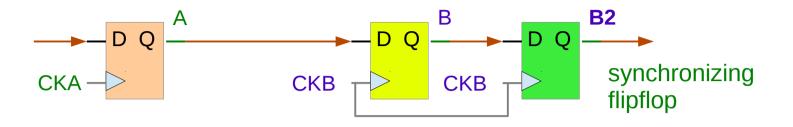

# Synchronizing FlipFlops

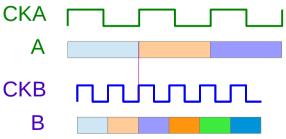

The likelihood of the synchronizing flipflop is <u>less</u> than that of the first flipflop going metastable.

Usually the metastable period is not so long compared to the clock period but the following case can happen

The probability never goes to zero

Metastable State (3C)

Young Won Lim 6/29/13

#### **NOR-based SR Latch**

#### References

[1] http://en.wikipedia.org/

[2] M. M. Mano, C. R. Kime, "Logic and Computer Design Fundamentals", 4<sup>th</sup> ed.

[3] J. Stephenson, Understanding Metastability in FPGAs. Altera Corporation white paper. July 2009.