# Device Power (2H)

Copyright (c) 2011-2016 Young W. Lim.

Permission is granted to copy, distribute and/or modify this document under the terms of the GNU Free Documentation License, Version 1.2 or any later version published by the Free Software Foundation; with no Invariant Sections, no Front-Cover Texts, and no Back-Cover Texts. A copy of the license is included in the section entitled "GNU Free Documentation License".

Please send corrections (or suggestions) to youngwlim@hotmail.com.

This document was produced by using OpenOffice and Octave.

#### Power

#### **Static Power Dissipation**

- Sub threshold condition when the transistors are off.

- Tunnelling current through gate oxide.

- Leakage current through reverse biased diodes.

- Contention current in ratioed circuit

#### **Dynamic Power Dissipation**

- Charging and discharging of load capacitances.

- Short circuit power dissipation

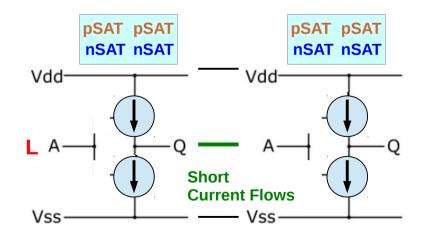

#### Short Circuit Power Dissipation

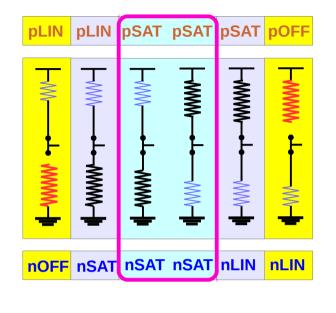

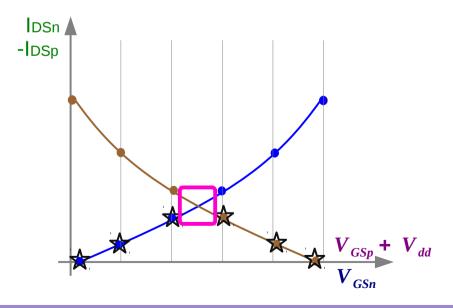

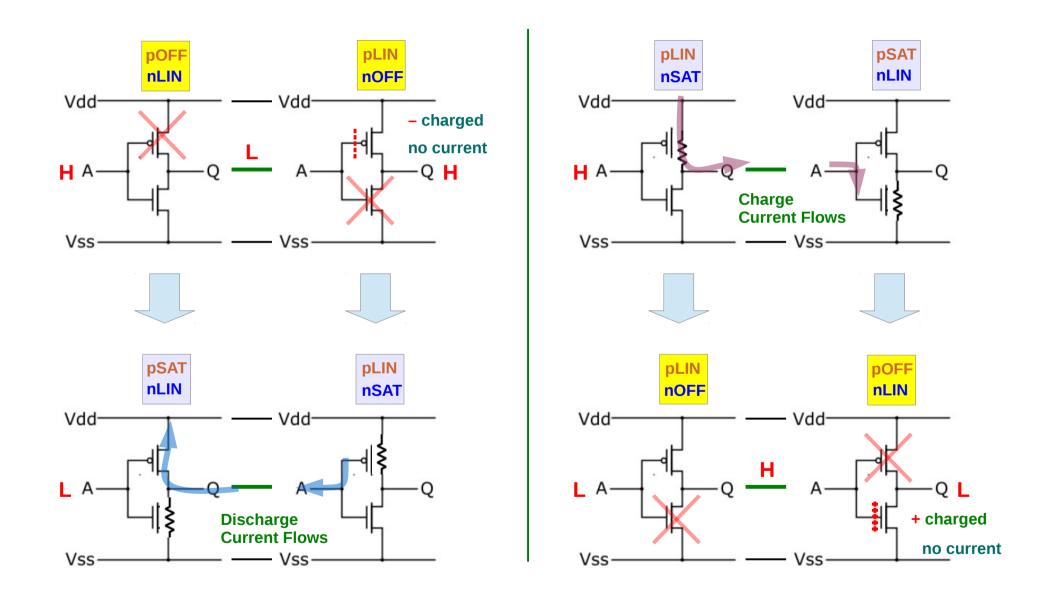

Since there is a finite rise/fall time for both pMOS and nMOS, during transition, for example, from off to on, both the transistors will be on for a small period of time in which current will find a path directly from VDD to ground, hence creating a short circuit current.

Short circuit power dissipation increases with rise and fall time of the transistors.

## Charging and Discharging Load Capacitance (1)

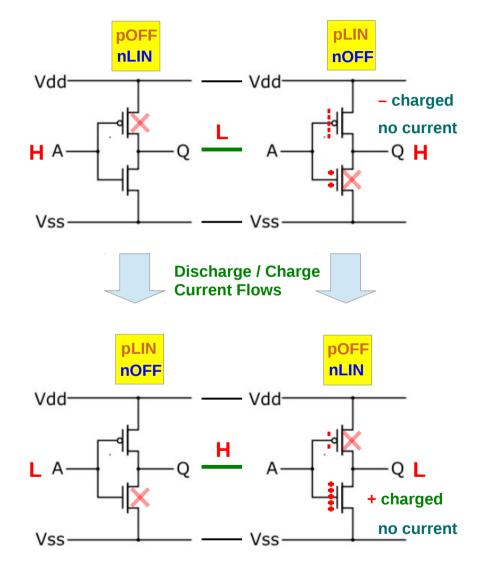

CMOS circuits dissipate power by charging the various load capacitances (mostly gate and wire capacitance, but also drain and some source capacitances) whenever they are switched.

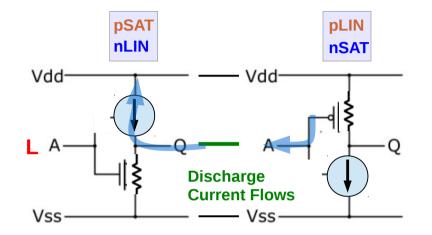

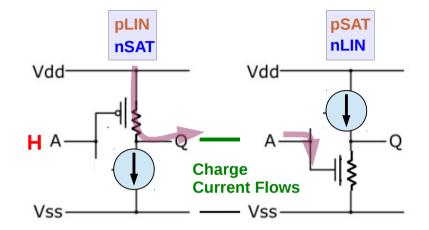

In one complete cycle of CMOS logic, current flows from VDD to the load capacitance to **charge** it and then flows from the charged load capacitance to ground during **discharge**.

## Charging and Discharging Load Capacitance (2)

**Device Power (2H)**

6

### Charging and Discharging Load Capacitance (3)

**Device Power (2H)**

### Charging and Discharging Load Capacitances (4)

Therefore in one complete charge/discharge cycle, a total of  $Q=C_{L}V_{DD}$  is thus transferred from  $V_{DD}$  to ground.

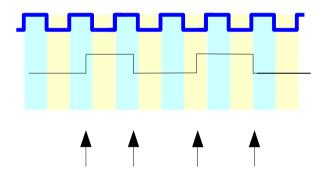

Multiply by the switching frequency on the load capacitances to get the current used, and multiply by voltage again to get the characteristic switching power dissipated by a CMOS device:  $P = C V^2 f$ .

Since most gates do not operate/switch at every clock cycle, they are often accompanied by a factor  $\alpha$ , called the activity factor. Now, the dynamic power dissipation may be re-written as  $P = \alpha C V^2 f$ .

Static Power Source Subthreshold Leakage Gate Leakage Junction Leakage Contention Current

Static Power Estimation

Multiple Threshold Voltages and Oxide thickness Variable Threshold Voltages Input Vector Control

#### **Dynamic Power**

Minimize Capacitance Minimize Short Circuit Current

#### References

- [1] http://en.wikipedia.org/

- [2] http://www.allaboutcircuits.com/

- [3] W. Wolf, "Modern VLSI Design : Systems on Silicon

- [4] N. Weste, D. Harris, "CMOS VLSI Design: A Circuits and Systems Perspective"

- [5] J. P. Uyemura, "Introduction to VLSI Circuits and Systems"

- [6] https://en.wikiversity.org/wiki/The\_necessities\_in\_SOC\_Design

- [7] https://en.wikiversity.org/wiki/The\_necessities\_in\_Digital\_Design

- [8] https://en.wikiversity.org/wiki/The\_necessities\_in\_Computer\_Design

- [9] https://en.wikiversity.org/wiki/The\_necessities\_in\_Computer\_Architecture

- [10] https://en.wikiversity.org/wiki/The\_necessities\_in\_Computer\_Organization

- [11] https://en.wikiversity.org/wiki/Verilog\_programming\_in\_plain\_view