Timer

The 555 timer IC is an integrated circuit (chip) used in a variety of timer, pulse generation, and oscillator applications. The 555 can be used to provide time delays, as an oscillator, and as a flip-flop element. Derivatives provide two (556) or four (558) timing circuits in one package.[2]

Construction

The IC was designed in 1971 by Hans R. Camenzind under contract to Signetics (later acquired by Philips Semiconductors, and now NXP).

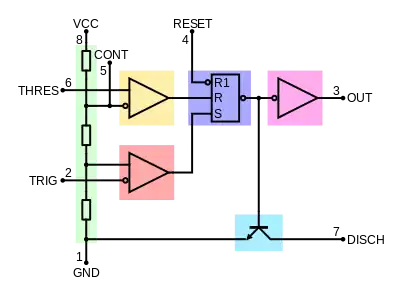

555 internal schematic of bipolar version |

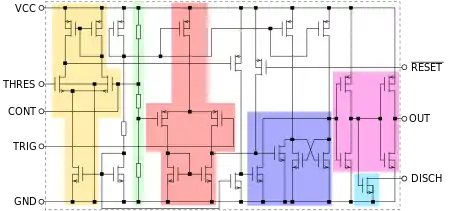

555 internal schematic of CMOS version |

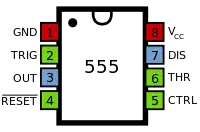

Symbol & Pins

The typical pinout of the 555 and 556 IC packages are as follows

555 Pin# 556 Pin# Pin Name Pin Purpose 1 7 GND Ground supply - ground reference voltage (zero volts). 2 6, 8 TRIG Trigger - the OUT pin goes high and a timing interval starts when this input falls below 1⁄2 of CTRL voltage (which is typically 1⁄3 VCC, CTRL being 2⁄3 VCC by default if CTRL is left open). More simply we can say that OUT will be high as long as the trigger is kept at low voltage. Output of the timer totally depends upon the amplitude of the external trigger voltage applied to this pin. 3 5,9 OUT Output - the push-pull (P.P.) output is driven to GND or approximately 1.7 V below +VCC. (Note: CMOS timer parts can drive output up to VCC rail.) Signetics recommends a 1 nF decoupling capacitor be connected at the output pin in circuits that connect to digital logic inputs, which may help minimize 555 output switching noise from causing problems 4 4,10 RESET Reset - a timing interval may be reset by driving this input to GND, but the timing does not begin again until RESET rises above approximately 0.7 volts. Overrides TRIG which overrides THR. (THR instead overrides TRIG on the LM555) 5 3,11 CTRL Control (or Control Voltage or CV) - provides "control" access to the internal voltage divider (by default is 2⁄3 VCC). By applying a voltage to the CONTROL VOLTAGE input one can alter the timing characteristics of the device. In most applications, this pin is not used, thus it's recommended to connect a low-noise 10 nF decoupling capacitor (film or C0G ceramic) between Control pin and Ground pin to filter noise on the higher reference voltage . The control pin input can be used to build an astable multivibrator with a frequency-modulated output. 6 2,12 THR Threshold - the timing (OUT high) interval ends when the voltage at THR ("threshold") is greater than that at CTRL (2⁄3 VCC if CTRL is open). Overrides TRIG on the LM555 7 1,13 DIS Discharge - open-collector output which may discharge a capacitor between intervals. In phase with output. 8 14 VCC Positive supply - the guaranteed voltage range of bipolar parts are typically 4.5 volt to 15 volts (some parts rated up to 16 volts or 18 volts), though most bipolar parts will operate at voltages as low as 3 volts. (Note: CMOS timer parts have a lower minimum voltage rating.) It's recommended that a 100 nF decoupling capacitor be connected as close as possible to this pin and optionally a 10 to 100 uF reservoir capacitor depending on the size of the load on the output pin. These capacitance values are a starting point for consideration instead of mandatory values that must be used.

Operation

The IC 555 has three operating modes:

1.Astable (free-running) mode – the 555 can operate as an electronic oscillator. Uses include LED and lamp flashers, pulse generation, logic clocks, tone generation, security alarms, pulse position modulation and so on. The 555 can be used as a simple ADC, converting an analog value to a pulse length (e.g., selecting a thermistor as timing resistor allows the use of the 555 in a temperature sensor and the period of the output pulse is determined by the temperature). The use of a microprocessor-based circuit can then convert the pulse period to temperature, linearize it and even provide calibration means.

2.Monostable mode – in this mode, the 555 functions as a "one-shot" pulse generator. Applications include timers, missing pulse detection, bounce-free switches, touch switches, frequency divider, capacitance measurement, pulse-width modulation (PWM) and so on.

3.Bistable (schmitt trigger) mode – the 555 can operate as a flip-flop, if the DIS pin is not connected and no capacitor is used. Uses include bounce-free latched switches.

Astable

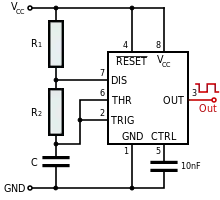

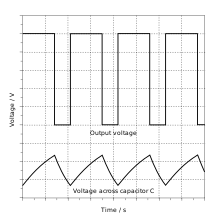

In astable mode, the 555 timer puts out a continuous stream of rectangular pulses having a specified frequency. Resistor R1 is connected between VCC and the discharge pin (pin 7) and another resistor (R2) is connected between the discharge pin (pin 7), and the trigger (pin 2) and threshold (pin 6) pins that share a common node. Hence the capacitor is charged through R1 and R2, and discharged only through R2, since pin 7 has low impedance to ground during output low intervals of the cycle, therefore discharging the capacitor.

In the astable mode, the frequency of the pulse stream depends on the values of R1, R2 and C:

The high time from each pulse is given by:

and the low time from each pulse is given by:

where R1 and R2 are the values of the resistors in ohms and C is the value of the capacitor in farads.

The power capability of R1 must be greater than .

Particularly with bipolar 555s, low values of must be avoided so that the output stays saturated near zero volts during discharge, as assumed by the above equation. Otherwise the output low time will be greater than calculated above. The first cycle will take appreciably longer than the calculated time, as the capacitor must charge from 0V to 2⁄3 of VCC from power-up, but only from 1⁄3 of VCC to 2⁄3 of VCC on subsequent cycles.

To have an output high time shorter than the low time (i.e., a duty cycle less than 50%) a fast diode (i.e. 1N4148 signal diode) can be placed in parallel with R2, with the cathode on the capacitor side. This bypasses R2 during the high part of the cycle so that the high interval depends only on R1 and C, with an adjustment based the voltage drop across the diode. The voltage drop across the diode slows charging on the capacitor so that the high time is a longer than the expected and often-cited ln(2)*R1C = 0.693 R1C. The low time will be the same as above, 0.693 R2C. With the bypass diode, the high time is

where Vdiode is when the diode's "on" current is 1⁄2 of Vcc/R1 which can be determined from its datasheet or by testing. As an extreme example, when Vcc= 5 and Vdiode= 0.7, high time = 1.00 R1C which is 45% longer than the "expected" 0.693 R1C. At the other extreme, when Vcc= 15 and Vdiode= 0.3, the high time = 0.725 R1C which is closer to the expected 0.693 R1C. The equation reduces to the expected 0.693 R1C if Vdiode= 0.

The operation of RESET in this mode is not well-defined. Some manufacturers' parts will hold the output state to what it was when RESET is taken low, others will send the output either high or low.

The astable configuration, with two resistors, cannot produce a 50% duty cycle. To produce a 50% duty cycle, eliminate R1, disconnect pin 7 and connect the supply end of R2 to pin 3, the output pin. This circuit is similar to using an inverter gate as an oscillator, but with fewer components than the astable configuration, and a much higher power output than a TTL or CMOS gate. The duty cycle for either the 555 or inverter-gate timer will not be precisely 50% and will change based off any load that the output is also driving while high (longer duty cycles for greater loads) due to the fact the timing network is supplied from the devices output pin, which has different internal resistances depending on whether it is in the high or low state (high side drivers tend to be more resistive).

Monostable

.png.webp)

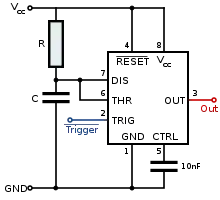

In monostable mode, the output pulse ends when the voltage on the capacitor equals 2⁄3 of the supply voltage. The output pulse width can be lengthened or shortened to the need of the specific application by adjusting the values of R and C

The output pulse width of time t, which is the time it takes to charge C to 2⁄3 of the supply voltage, is given by

where t is in seconds, R is in ohms (resistance) and C is in farads (capacitance).

While using the timer IC in monostable mode, the main disadvantage is that the time span between any two triggering pulses must be greater than the RC time constant. Conversely, ignoring closely spaced pulses is done by setting the RC time constant to be larger than the span between spurious triggers. (Example: ignoring switch contact bouncing.)

Bistable

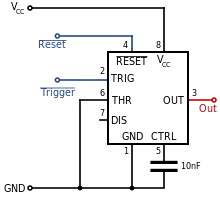

In bistable mode, the 555 timer acts as a basic flip-flop. The trigger and reset inputs (pins 2 and 4 respectively on a 555) are held high via pull-up resistors while the threshold input (pin 6) is simply floating. Thus configured, pulling the trigger momentarily to ground acts as a 'set' and transitions the output pin (pin 3) to VCC (high state). Pulling the reset input to ground acts as a 'reset' and transitions the output pin to ground (low state). No timing capacitors are required in a bistable configuration. Pin 7 (discharge) is left unconnected, or may be used as an open-collector output.

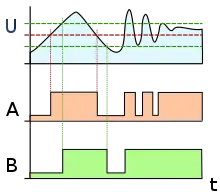

A 555 timer can be used to create a schmitt trigger which converts a noisy input into a clean digital output. The input signal should be connected through a series capacitor which then connects to the trigger and threshold pins. A resistor divider, from VCC to GND, is connected to the previous tied pins. The reset pin is tied to VCC.